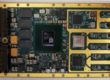

X3-25M Data Acquisition Board with 105MSPS Adcs, 50MSPS Dacs and Spartan 3A DSP FPGA

The X3-25M is an XMC IO module that can be fitted in a PC using a XMC to PCIe adapter or XMC to PCI adapter or a CompactPCI chassis using a XMC to CompactPCI adapter or a Standalone PC. Other hosting options include a standalone eInstrument and connection to a variety of PC hosts.

The data acquisition board has 2 channels of simultaneous 16 bit analogue to digital converters. The maximum sample rate that can be streamed to the host is 90MSPS on a single channel or 45MSPS 2 channels. The analogue inputs have a lowpass filter with cutoff at 75MHz, and a programmable gain amplifier which gives input ranges of +/-2V, +/-1V and +/-0.2V. The converter (LTC2207) is a pipelined successive approximation device.

The converters have a maximum conversion rate of 105MSPS but the interface to the onboard memory can only sustain ~180MB/s in and out functioning as a FIFO to the host. Therefore the converters can only be run above 90MSPS if a) only 1 channel is used, or b) if user logic is inserted to the data flow before the memory interface which decimates the data. For example a digital downconverter.

The board also has 2 channels of simultaneous 16 bit digital to analogue converters. These can be clocked at upto 50MSPS and have filters which give a 12.5MHz bandwidth and voltage range +/-2V. If streaming from the host via the memory direct to the DACs be aware that few hosts are able to sustain 180MB/s to XMC boards. The board can also be used to preload waveforms in the memory and play at full rate for a burst.

The X3-25M has an onboard PLL which can be driven by an onboard reference oscillator or by an offboard reference clock. Alternately the user can supply an external clock. Triggering of the start of samples can be done by software or an external active high LVTTL signal.

The X3-25M also has 44 bits of user digital IO. This can be read or written to as a 32 bit register from the host, or if the user modifies the logic, can be used to interface to a variety of digital devices such as serial, parallel ports, I2C devices etc. The Spartan3 device supports LVTTL.

Data acquisition control, signal processing, buffering, and system interface functions are implemented in a Xilinx Spartan3A DSP FPGA, 1.8M gate device. Two 512Kx32 memory devices are used for data buffering and FPGA computing memory. The data acquisition board has a single lane PCI Express interface to the host which can sustain 160MB/s to the host.

The X3-25M is supported by Malibu, a set of C++ libraries to use the board under Windows and Linux. This includes example programs to use the board to setup the logic, acquire samples and stream them to disk, and a Wave program to stream samples from host to Dacs.

The logic can be fully customized using VHDL and MATLAB using the FrameWork Logic toolset. The MATLAB BSP supports real-time hardware-in-the-loop development using the graphical, block diagram Simulink environment with Xilinx System Generator.