**FMC ADC 125**

## **Environmental information**

Operating temperature range: 0°c to 50°c Storage temperature range: -55°c to 125°c Maximum shock range: 10g during 20ms Maximum vibration range: 0.03 g2/Hz Compliant with ROHS process

# **Ordering information**

FMC-ADC-125

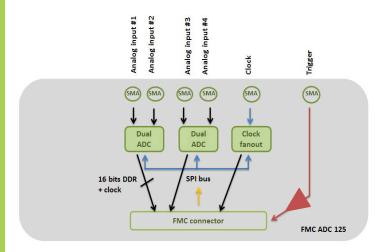

The TechwaY ADC125 mezzanine is a fully compliant FMC mezzanine (VITA 57.1) which offers four 16bits A/D channels up to 125 MSPS.

The ADC125 mezzanine is based on two dual Analog-to-Digital converters from Linear Technology: LTC2185. the

This mezzanine allows you to sample your signals with your own external sampling clock. You also get the capability to use the on-board sampling clock. A trigger input is available to be able to synchronize all channels with a 1 sample accuracy.

You are able to fine-tune the ADCs through the I<sup>2</sup>C bus. ADC gain, bias and delay can be set-up according to your needs. Temperature and power monitoring can be check directly from the FPGA.

19 avenue de Norvège – Villebon-sur-Yvette 91953 Courtabœuf Cedex - FRANCE Tél.: +33 (0)1 64 53 37 90 - Fax: +33 (0)1 64 53 17 74

GPS: 48°41′32″N - 2°12′53″E

Certificate FR12/695125

# **Applications**

Radar

Sonar Medical equipment

Aerospace and test measurement instruments

#### **Benefits**

Ready To Use FMC – VITA 57.1 – compliant

Easy To Use

Free SDK with example design

TechwaY support

Cost effective

## **Sales Enquiries**

Tél. +33 (0)1 64 53 37 90 Email : info@techway.eu www.techway.eu

#### **Features**

Four Sampling Channels

One common trigger input

One common sampling clock input

Internal programmable clock generator available

Selected sampling clock from external or local

16 bits resolution Input range: 1Vpp

Up to 125MHz sampling frequency

Up to 550MHz analog bandwidth (depend of

input analog stage) Up to 90dB SFDR Up to 77 dB SNR

DDR LVCMOS/LVDS outputs

# **Software Development Kit**

ADC set up Controlling the card by I2C

#### **Firmware**

VHDL ADC control module

## **Block Diagram**