Adapts PCIe XMC to PXI Express with P16 High Speed Communications Ports and Digital IO

V2.01

#### **FEATURES**

- Adapt one XMC PCI Express VITA 42.3 module to a PXI Express slot

- · Supports up to 8 lanes, PCle gen3

- Transparent Operation

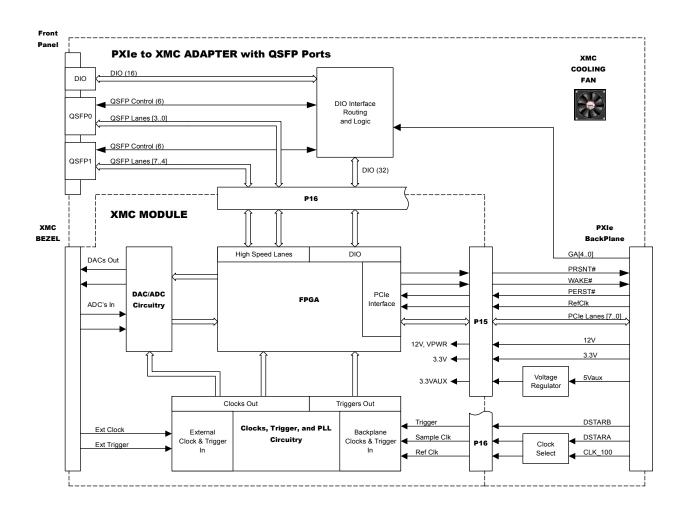

- Eight high-speed gigabit transceiver (GTH) lanes from XMC P16 exposed via dual, frontpanel QSFP connectors and 8 differential DIO pairs routed from P16 to a high-speed, frontpanel Samtec connector.

OR:

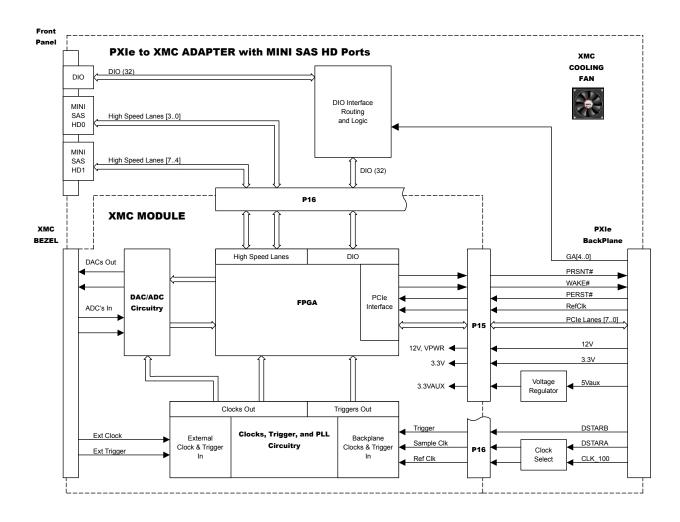

Eight high-speed gigabit transceiver (GTH) lanes from XMC P16 exposed via dual, front-panel MINI SAS HD connectors and 16 differential DIO pairs routed from P16 to a high-speed, front-panel Samtec connector.

- IEEE 1384 XMC mechanicals

- >50W power provided to the module

- · Robust end bracket

- · Dedicated fan provides 19 CFM air flow

- · Consumes two contiguous PXIe slots

- Supports newest Innovative XMC cards which provide 5 GHz analog I/O & use of the Kintex XCKU060/XCKU085 Ultrascale FPGA

### **APPLICATIONS**

- Add XMC modules to standard PXIe host systems

- System expansion using high speed serial links

### **SOFTWARE**

· No software required

#### **DESCRIPTION**

The PXI Express to XMC module adapter allows a standard 75 x 150mm PCIe XMC module to be used in a PXI Express slot. The XMC module must be VITA 42.3-compatible and may support up to eight PCI Express lanes. The adapter is completely transparent to PCI Express. All PCIe bus signals from the PXI Express host bus are connected directly to the XMC module (the PCIe clock is rebiased). The PXIe adapter can be utilized with Innovative XMC cards including our newest generation models which provide 5 GHz analog I/O and use the Kintex XCKU060/XCKU085 Ultrascale FPGA.

Two front panel configurations are available for XMC GTH transceivers and general purpose DIO:

QSFP option: Eight GTH transceivers from the XMC P16 connector are routed to two front-panel QSFP connectors to provide inter-FPGA communications at 10 GB/s. The connectors provide a simple way to "patch-panel" communications links between cards. Six DIO lines are routed from the XMC P16 connector to each QSFP control interface, and eight differential DIO pairs are routed to a separate high speed Samtec connector.

MINI SAS HD option: Eight GTH transceivers from the XMC P16 connector are routed to two front-panel MINI SAS HD connectors to provide inter-FPGA communications at 10 GB/s. The connectors provide a simple way to "patch-panel" communications links between cards. Sixteen differential DIO

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Innovative Integration products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Innovative Integration standard warranty. Production processing does not necessarily include testing of all parameters.

pairs are routed to a separate high speed Samtec connector.

Special support for trigger and timing inputs to Innovative XMC modules is provided through their front-panel SMA/SMMC connectors or PXIe backplane differential signals.

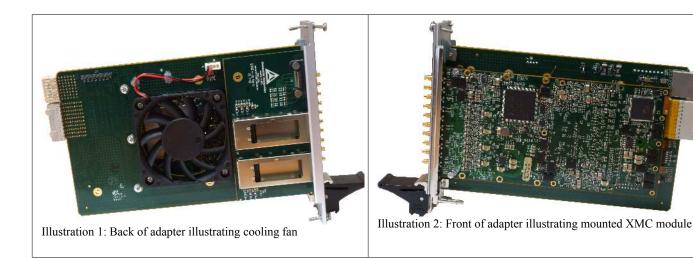

Convection cooling via a dedicated fan, provides cooling to the XMC module.

The XMC module mounts securely to the adapter using standoffs and with the end bracket. The bracket mates to standard PMC end brackets and supports an EMI gasket.

This electronics assembly can be damaged by ESD. Innovative Integration recommends that all electronic assemblies and components circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ORDERING INFORMATION**

| Product                                                                            | Part<br>Number | Description                                                                                                                                    |

|------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PXIe-XMC Adapter<br>with I/O expansion<br>for X6 modules<br>(QSFP Ports)           | 80341-1        | PXIe XMC x8 Lane Adapter for Innovative X6, XA and XU-series XMC modules, 3U 8HP (Fan unit w/QSFP, QSFP Control, and 8 differential DIO pairs) |

| PXIe-XMC Adapter<br>with I/O expansion<br>for X3 modules                           | 80341-2        | PXIe XMC x8 Lane Adapter for Innovative X3-series XMC modules, 3U 8HP (Fan unit and 8 differential DIO pairs)                                  |

| PXIe-XMC Adapter<br>with I/O expansion<br>for X6 modules<br>(MINI SAS HD<br>Ports) | 80341-5        | PXIe XMC x8 Lane Adapter for Innovative X6, XA and XU-series XMC modules, 3U 8HP (Fan unit w/MINI SAS HD, and 16 differential DIO pairs)       |

## **Adapter Block Diagram with QSFP Ports (with Typical XMC Module)**

## Adapter Block Diagram with MINI SAS HD Ports (with Typical XMC Module)

| Physicals   |                           |  |

|-------------|---------------------------|--|

| Form Factor | PXI Express 3U, dual-slot |  |

| Size        | 3.72 in x 8.05 in         |  |

| Weight      | 100g                      |  |

| Power Capability Delivered to the XMC (from backplane) |                            |  |

|--------------------------------------------------------|----------------------------|--|

| Volts                                                  | Amps                       |  |

| 3.3V                                                   | 6A Maximum                 |  |

| 5VAUX (makes XMC 3.3VAUX)                              | 1A Maximum, to XMC 3.3VAUX |  |

| +12V 4A Maximum, to +12V & VPWR                        |                            |  |

| -12V                                                   | Not provided to XMC        |  |

<sup>\*\*</sup> XMC cooling may be required

### **DIO Signal Mapping for**

### X6, XA, XU families

| XMC       | X6                                | J3<br>DIO PORT | X6                                 | XMC       |

|-----------|-----------------------------------|----------------|------------------------------------|-----------|

| P16<br>C1 | DGND 3                            | 3 4            | DGND<br>DIO P4                     | P16<br>C5 |

| C2<br>F1  | DIO_N0 5 DGND 7 DIO_P1 9          | 7 8            | 6 DIO_N4<br>8 DGND<br>10 DIO P5    | C6<br>F5  |

| F2        | DIO N1 11                         | 11 12          | 12 DIO N5                          | F6        |

| F4<br>F3  | DIO NS 15<br>DIO P3 17            | 15 16          | 16 BIO N7<br>18 DIO P7             | F8<br>F7  |

| C4<br>C3  | DGND 19<br>DIO N2 21<br>DIO_P2 23 | 19 20<br>21 22 | 22 DGND<br>DIO N8<br>24 DIO_P6     | C8<br>C7  |

|           | DGND 25                           | 25 26          | 26 DGND<br>ERF8-013-01-L-D-RA-L-TR |           |

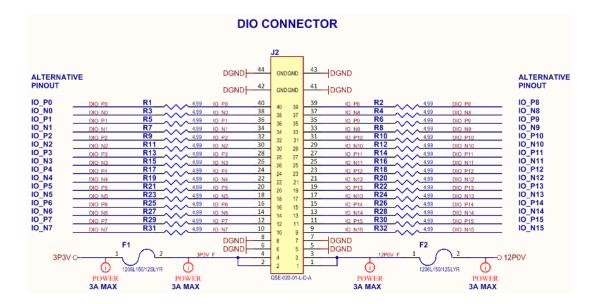

### **QSFP DIO Configuration**

#### J3 - Front Panel Connector for XMC DIO

DIO Signals are routed as 8 differential pairs. Pairs are 50 ohm, 100 ohm differential characteristic impedance, suitable for LVDS or LVPECL. These signals can also be used as single ended LVCMOS or LVTTL according to the configuration of the XMC module.

Connector: Samtec ERF8-013-01-L-D-RA-L-TR

Mating cables:

Samtec ERCD-013 series or equivalent (coax ribbon type for single ended signals)

Samtec ERDP-013 series or equivalent (twinax ribbon type for differential signals)

### **DIO Signal Mapping for X3 family**

| XMC<br>P16 | X3<br>DIO    | J3<br><u>DIO POR</u> T            |                         | X3<br>DIO                          | XMC<br>P16     |            |

|------------|--------------|-----------------------------------|-------------------------|------------------------------------|----------------|------------|

| C1<br>C2   | DIO0<br>DIO1 | DGND 3 DIO N0 5                   | 1 2<br>3 4<br>5 6       | 2 DGND<br>4 DIO P4<br>6 DIO N4     | DIO8<br>DIO9   | C9<br>C10  |

| C3<br>C4   | DIO2<br>DIO3 | DGND 9<br>DIO P1 9                | 7 8<br>9 10<br>11 12    | 8 DGND<br>10 DIO P5<br>12 DIO N5   | DIO10<br>DIO11 | C11<br>C12 |

| C8<br>C7   | DIO7<br>DIO6 | DGND 13<br>DIO N3 15<br>DIO P3 17 | 13 14<br>15 16<br>17 18 | 14 DGND<br>16 DIO N7               | DIO15<br>DIO14 | C16<br>C15 |

| C6<br>C5   | DIO5<br>DIO4 | DGND 21<br>DIO P2 23              | 19 20<br>21 22<br>23 24 | 20 DGND<br>22 DGND<br>24 DIO N6    | DIO13<br>DIO12 | C14<br>C13 |

|            |              | DGND 25                           | 25 26                   | 26 DGND<br>ERF8-013-01-L-D-RA-L-TR |                |            |

### J1 & J2 Front Panel Connectors for QSFP0 & QSFP1

| XMC High Speed<br>Serial Pair | XMC P16 Pins<br>(P/N) | QSFP Connectors (0 and 1) |

|-------------------------------|-----------------------|---------------------------|

| TXP0/N0                       | A1/B1                 | 0: TXP0/N0                |

| TXP1/N1                       | D1/E1                 | 0: TXP1/N1                |

| TXP2/N2                       | A3/B3                 | 0: TXP2/N2                |

| TXP3/N3                       | D3/E3                 | 0: TXP3/N3                |

| TXP4/N4                       | A5/B5                 | 1: TXP0/N0                |

| TXP5/N5                       | D5/E5                 | 1: TXP1/N1                |

| TXP6/N6                       | A7/B7                 | 1: TXP2/N2                |

| TXP7/N7                       | D7/E7                 | 1: TXP3/N3                |

| RXP0/N0                       | A11/B11               | 0: RXP0/N0                |

| RXP1/N1                       | D11/E11               | 0: RXP1/N1                |

| RXP2/N2                       | A13/B13               | 0: RXP2/N2                |

| RXP3/N3                       | D13/E13               | 0: RXP3/N3                |

| RXP4/N4                       | A15/B15               | 1: RXP0/N0                |

| RXP5/N5                       | D15/E15               | 1: RXP1/N1                |

| RXP6/N6                       | A17/B17               | 1: RXP2/N2                |

| RXP7/N7                       | D17/E17               | 1: RXP3/N3                |

Connector: TE Connectivity 1761987-9

Housing: TE\_Connectivity 1888781-1

Mating Cable: (Standard QSFP Cable)

### **MINI SAS HD DIO Configuration**

#### J2 - Front Panel Connector for XMC DIO

DIO Signals are routed as 16 differential pairs. Pairs are 50 ohm, 100 ohm differential characteristic impedance, suitable for LVDS or LVPECL. These signals can also be used as single ended LVCMOS or LVTTL according to the configuration of the XMC module.

Connector: Samtec QSE-020-01-L-D-A

Mating cable:

Samtec EQCD-020 series or equivalent (coax ribbon type for single ended signals)

### J1 Front Panel Connector for MINI SAS HD Ports 0 & 1

| XMC High Speed<br>Serial Pair | XMC P16 Pins (P/N) | MINI SAS HD Connector<br>(Ports 0 and 1) |

|-------------------------------|--------------------|------------------------------------------|

| TXP0/N0                       | A1/B1              | 0: TXP0/N0                               |

| TXP1/N1                       | D1/E1              | 0: TXP1/N1                               |

| TXP2/N2                       | A3/B3              | 0: TXP2/N2                               |

| TXP3/N3                       | D3/E3              | 0: TXP3/N3                               |

| TXP4/N4                       | A5/B5              | 1: TXP0/N0                               |

| TXP5/N5                       | D5/E5              | 1: TXP1/N1                               |

| TXP6/N6                       | A7/B7              | 1: TXP2/N2                               |

| TXP7/N7                       | D7/E7              | 1: TXP3/N3                               |

| RXP0/N0                       | A11/B11            | 0: RXP0/N0                               |

| RXP1/N1                       | D11/E11            | 0: RXP1/N1                               |

| RXP2/N2                       | A13/B13            | 0: RXP2/N2                               |

| RXP3/N3                       | D13/E13            | 0: RXP3/N3                               |

| RXP4/N4                       | A15/B15            | 1: RXP0/N0                               |

| RXP5/N5                       | D15/E15            | 1: RXP1/N1                               |

| RXP6/N6                       | A17/B17            | 1: RXP2/N2                               |

| RXP7/N7                       | D17/E17            | 1: RXP3/N3                               |

Connector: Amphenol G40H12331HR

Mating Cable: 3M 8US4-AA119 series

or 3M 8US4-CB119 series

or equivalent

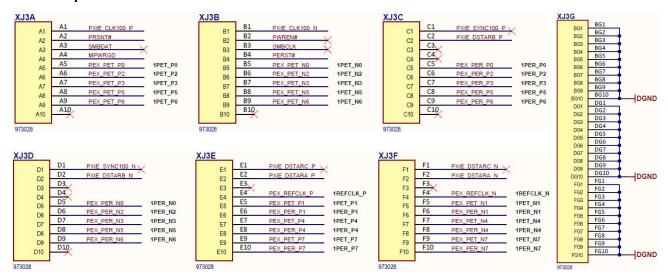

### XJ4 - Backplane Connector

### XJ3 - Backplane Connector

#### XJ4 and XJ3 signal usage notes

Routed directly to corresponding XMC P15/P16 signals: PEX\_PET, PEX\_PER, PEX\_REFCLK, PERST# (PCI Express); WAKE#; PRSNT#; and PXIe DSTARB (trigger)

Available for XMC sample clock or PLL reference: PXIE CLK100 and PXIE DSTARA

### XJ4 and XJ3 signal usage notes (cont'd)

Not Used: PXI\_TRIGn, PXI\_STAR, PXI\_CLK10 (triggers with 10MHz resolution); SYSEN#; ALERT#; ATNLED; PXI\_LBL6; PXI\_LBR6; SMBDAT; SMBCLK; PWREN#; PXIE\_SYNC100; and PXIE\_STARC

Pulled up to 3.3V: ATNSW# (always idle); and MPWRGD (always good)

Routed to DIO inputs of XMC: GA[4..0] (slot ID information)

### **Applications Information**

### **High Speed Serial Communications**

The adapter card has 8 high speed serial lanes from the XMC card via P16 supporting Gigabit serial ports for intercard communications or expansion. The serial lanes connect directly to QSFP connectors (or MINI SAS HD connectors). Standard QSFP cables (MINI SAS HD cables) can be used to connect multiple cards together to create high speed, dedicated communications channels between XMC modules. On Innovative's XA, X6 and XU modules, these are multi-gigabit ports directly from the XMC Virtex FPGA.

### **Digital IO**

Digital IO from XMC P16 is directly mapped to the Samtec connector on the adapter front panel. There are 8 differential pairs (100 ohm) with matched length for the QSFP version, 16 differential pairs (100 ohm) with matched length for the MINI SAS HD version. Mating cables suitable for high-speed differential pairs are available.

#### **Cooling the XMC Module**

Many XMC modules require special considerations to provide adequate cooling. Monitor XMC module device temperatures and add convective air flow if required to maintain within rated thermal limits.

The module provides a conduction cooling path for XMC modules employing a VITA20-compliant heat spreader and dedicated thermal plane. The conduction cooling conforms to VITA20 specification for PMC/XMC module cooling. When a compatible module/spreader is used with the card, the adapter thermal plane effectively conducts heat from the module to the carrier card and front bracket. System cooling is therefore more effective because of the heat spreading from the module to the carrier card. However, this conductive path is insufficient for highly-dissipative XMC modules.

A fan is included on the PXIe-XMC adapter for cooling. The fan provides approximately 19 CFM air flow. When the fan is installed, it blows air directly on the module and is very effective. The fan protrudes 10mm from the back of the card and intrudes into the adjacent slot in the PXIe chassis. Hence, the adapter and fan are said to consume two PXIe slots.

#### **Module Mounting Hardware**

The module can be securely mounted to the adapter for both conduction cooling and ruggedness. Two 10mm female threaded standoffs are used to secure the module to the adapter. If conduction cooling is used, cooling bars are secured to the card and the module using 2.5 mm screws. This hardware can be purchased from Innovative Integration.

### **Software Driver**

No software is required.

### **Switch Settings**

### SW1 – Sample Clock Settings (for the clock supplied to P16 of the XMC Module)

| Switch Number | Function                                                                                       | Settings                                                                    |  |

|---------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| 1             | Clock Source Select (from PXIe Backplane)                                                      | On = PXIE_CLK100<br>Off = PXIE_DSTARA                                       |  |

| 2             | Sample Clock Enable Always On except when switch #3 is On                                      | On = Supply clock to XMC P16-A9, B9 Off = Do not supply clock to P16-A9, B9 |  |

| 3             | Reference Clock Enable On only when using the PLL of an X3 family XMC Module                   | On = Supply clock to XMC P16-D9, E9 Off = Do not supply clock on P16-D9, E9 |  |

| 4             | Signal Type (to XMC Module) Always On, because all Innovative Integration XMC Modules use LVDS | On = Clock signal is LVDS Off = Clock signal is LVPECL                      |  |

If an XMC Module from another manufacturer is used, recommendations in the "Function" column may not apply, and settings should be made according to the information in the "Settings" column.

### SW2 - Fan Speed Control (Not Applicable to Adapter -0 version)

Fan Speed Control is not currently implemented; the fan always runs at full speed. Therefore the settings of SW2 are "Don't Care". Contact the factory if fan speed control is required.

Note: Adapter -0 version does not have a fan.

### SW3 - VCCIO Voltage Selection and routing for Geographic Address (Adapter -0 version only)

| Switch Number | Function                                                   | Settings                                  |

|---------------|------------------------------------------------------------|-------------------------------------------|

| 1             | VCCIO Voltage Selection                                    | 1.5V = 1 & 2  Off                         |

| 2             | 1.8V: for XU family<br>2.5V: for X6, X3, X5, & XA families | 1.8V = 1  On;  2  Off<br>2.5V = 1 & 2  On |

| 3             | Geographic Address routing                                 | X5 (except X5-COM) = 3 Off, 4 On          |

| 4             |                                                            | All Other families = 3 On, 4 Off          |

This switch applies only to Adapter -0 versions because the other Adapter versions have a mezzanine assembly matched to the installed XMC that accounts for these Voltage Selection and Geographic routing requirements.

### **IMPORTANT NOTICES**

Innovative Integration Incorporated reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Innovative Integration's terms and conditions of sale supplied at the time of order acknowledgment.

Innovative Integration warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with Innovative Integration's standard warranty. Testing and other quality control techniques are used to the extent Innovative Integration deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Innovative Integration assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using Innovative Integration products. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

Innovative Integration does not warrant or represent that any license, either express or implied, is granted under any Innovative Integration patent right, copyright, mask work right, or other Innovative Integration intellectual property right relating to any combination, machine, or process in which Innovative Integration products or services are used. Information published by Innovative Integration regarding third-party products or services does not constitute a license from Innovative Integration to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Innovative Integration under the patents or other intellectual property of Innovative Integration.

Reproduction of information in Innovative Integration data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice.

Innovative Integration is not responsible or liable for such altered documentation. Resale of Innovative Integration products or services with statements different from or beyond the parameters stated by Innovative Integration for that product or service voids all express and any implied warranties for the associated Innovative Integration product or service and is an unfair and deceptive business practice. Innovative Integration is not responsible or liable for any such statements.

For further information on Innovative Integration products and support see our web site:

www.innovative-dsp.com

Mailing Address: Innovative Integration, Inc.

741 Flynn Rd, Camarillo, CA 93012

Copyright ©2007, Innovative Integration, Incorporated