FPGA Manager Gigabit Ethernet

click image to enlarge

Overview

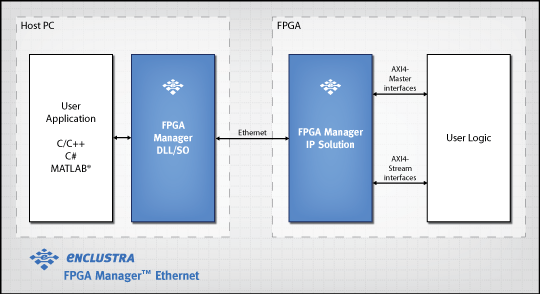

Enclustra’s FPGA Manager Ethernet solution allows for easy and efficient data transfer between a host and a FPGA over an Ethernet interface.

The solution includes a host software library (a Windows DLL or Linux static library), and a suitable IP core for the FPGA. The user host application can communicate with the FPGA through a simple API consisting of simple read/write data commands hiding the complexity of the underlying protocols. Both streaming and memory-mapped access are supported.

Highlights

- High-throughput, plug & play Ethernet interface

- Up to 120 MByte/sec data transfer rate

- Runs on Windows and Linux

- Supports C, C++, C# and MATLAB® user applications

- No recurring license fees

- Vendor-independent

Benefits

- Complete and easy to use solution for communication between FPGA and host

- No need for dealing with complexity of underlying protocols

- Evaluation kits and reference design available

- Highly configurable

Features

- Streaming data transfer between FPGA and host

- Memory-mapped access to

FPGA AXI or Avalon bus - Up to 16 independent bidirectional data channels

- Easy firmware Flash update capability

- Tri-speed Ethernet (10/100/1000 Mbit/sec)

- Includes a full license of the UDP/IP Ethernet IP Core

Deliverables

- FPGA Manager Ethernet IP Core

- VHDL source files (plain or encrypted, depending on product options)

- Reference design

- User manual

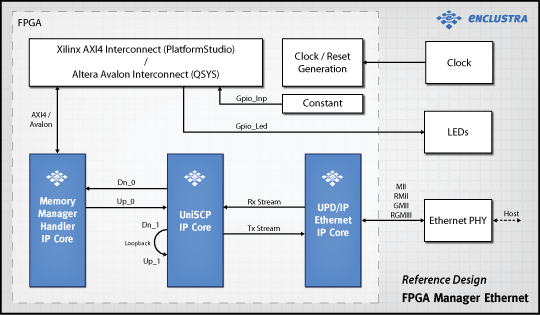

- FPGA Manager Ethernet IP Core Reference Design

- Reference design top-level VHDL file (plain VHDL)

- UCF / XDC / SDC constraint files (depending on product options)

- Xilinx® ISE / Xilinx Vivado™ / Intel® Quartus® project files (depending on product options)

- Top-level simulation test bench file (plain VHDL)

- Top-level simulation ModelSim project file

- Documentation

- Enclustra Ethernet Host Library

- Binary DLL

- API header files

- API User Manual

Site License Model

- The license is granted to an “authorized site”, meaning a single geographical location with radius < 5 km in which the licensee conducts business.

- The licensed material can be used for unlimited projects and/or end products developed at the authorized site.

Reference Design

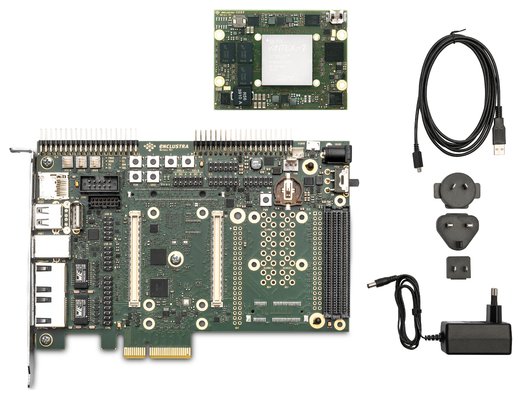

FPGA Manager Evaluation Kit

click image to enlarge

| The FPGA Manager Evaluation Kit provides a full featured design platform to build communication centric applications for PCIe, Ethernet and USB 3.0. The kit provides an out-of-the box hardware platform with reference design to both speed your development time and enhance your productivity. It contains following components: | ||

|

1: Included only once per Site and Year.

Product Selection Matrix

| Product Code | Description |

|---|---|

| EN-MGR-BASE1 | Base license, 2 streaming channels, DMA |

| EN-MGR-OPT-XIL | Xilinx FPGA support |

| EN-MGR-OPT-ALT | Intel FPGA support |

| EN-MGR-OPT-ETH1G2 | Trispeed ethernet support |

| EN-MGR-OPT-WIN | Windows Support (C/C++/.NET) (PCIe/Ethernet/USB) |

| EN-MGR-OPT-LIN | Linux Support (C/C++) (PCIe/Ethernet) |

| EN-MGR-OPT-ADV | Advanced features: 16 channels, multi-width and more |

| EN-MGR-OPT-HLL | Higher-level language support: MATLAB (others upon customer request) |

Target Applications

- Test & Measurement

- Image Processing

- Smart Cameras

- Software Defined Radio