click image to enlarge

Overview

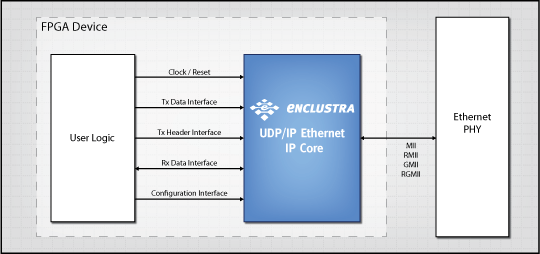

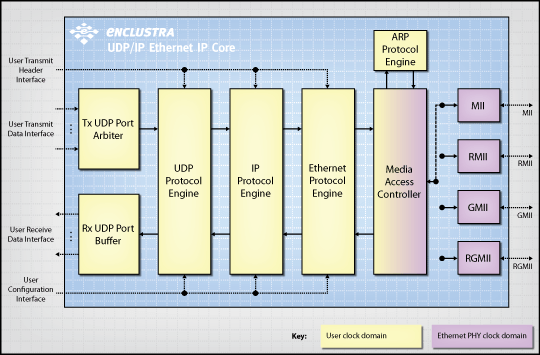

Enclustra’s UDP/IP Ethernet IP core is optimized for Intel (Altera) and Xilinx FPGAs and easily enables FPGA-based subsystems to communicate with other subsystems via Ethernet, using the UDP protocol. The IP core is highly configurable and optimally implemented for the use in current Intel® and Xilinx® FPGA architectures. It provides a simple to use interface to the user logic, and supports the common media independent interfaces MII, RMII, GMII and RGMII. With its 8-bit wide transmit and receive interfaces running at 125 MHz, the IP core is able to operate at full 1 Gbit/sec wire speed. 100 Mbit/sec and 10 Mbit/sec operation is also supported.

Highlights

- Operates at full 1Gbit/sec wire speed

- Complete UDP, IPv4 and Ethernet layer processing

- Automatic ARP reply generation

- Header pass-through mode:

- Selectively override default UDP/IP/ETH header field values with values embedded in the transmit data stream

- Selectively embed UDP/IP/ETH header field values in the receive data stream for easy delivery to the user application

Benefits

- Standard UDP communication with FPGA-based systems

- Full 1 Gbit/sec wire speed can be achieved

- Low FPGA resource usage

Features

- 1 Gbit/sec, 100 Mbit/sec and 10 Mbit/sec operation

- MII, RMII, GMII and RGMII media independent interfaces (full-duplex only)

- Destination UDP port, destination IP address and destination MAC address filtering

- UDP checksum calculation and check

- Ethernet frame check

- Multiple UDP ports with dedicated receive and transmit interfaces for each port

- Optional receive data buffers

- Raw Ethernet port for non-UDP communication

Architecture

click image to enlarge

Evaluation Kit

click image to enlarge

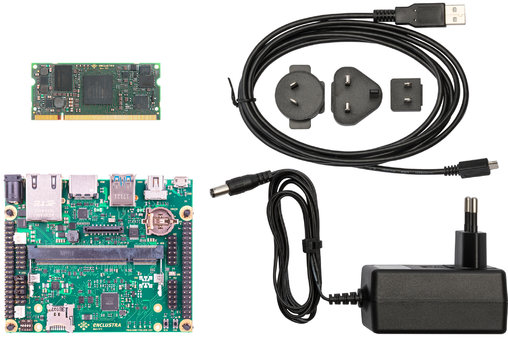

The UDP/IP Ethernet IP Core Evaluation Kit provides a full featured design platform to build communication centric applications for Ethernet. The kit provides an out-of-the box hardware platform with reference design, to reduce development time and allow you to focus on your target application. The kit is comprised of:

- UDP/IP Ethernet IP Core, Evaluation License

- Encrypted VHDL

- 1-hour time bomb

- Mars AX3 FPGA module (MA-AX3-35-1I-D8)

- Mars ST3 base board (MA-ST3)

- Reference design

- Two hours of support included1

1: Included only once per Site and Year.

Product Selection Matrix

| Product Code | Description |

|---|---|

| EN-UDP-IP-ETH-BASE1 | UDP/IP Ethernet IP Core |

| EN-UDP-IP-ETH-OPT-XIL | Xilinx FPGA support |

| EN-UDP-IP-ETH-OPT-ALT | Intel FPGA support |

| EN-UDP-IP-ETH-OPT-ETH1G | Ethernet Trispeed 10/100/1000 Mbps |

| EN-UDP-IP-ETH-OPT-MII | MII interface (10/100 Mbps) |

| EN-UDP-IP-ETH-OPT-RMII | RMII interface (10/100 Mbps) |

| EN-UDP-IP-ETH-OPT-GMII | GMII interface (10/100/1000 Mbps) |

| EN-UDP-IP-ETH-OPT-RGMII | RGMII interface (10/100/1000 Mbps) |

Deliverables

- UDP/IP Ethernet IP Core

- VHDL source files (plain or encrypted, depending on product options)

- Reference design

- User manual

- UDP/IP Ethernet IP core reference design

- Reference design top-level VHDL file (plain VHDL)

- UCF / XDC / SDC constraint files (depending on product options)

- Xilinx® ISE / Xilinx Vivado™ / Intel® Quartus® project files (depending on product options)

- Top-level simulation test bench file (plain VHDL)

- Top-level simulation ModelSim project file

- Documentation

Site Licence Model

- The license is granted to an “authorized site”, meaning a single geographical location with radius < 5 km in which the licensee conducts business.

- The licensed material can be used for unlimited projects and/or end products developed at the authorized site.

Target Applications

- Embedded Computing

- Data Acquisition

- High-Speed Communications

- Drive/Motion Control

- Digital Signal Processing

- Image Processing

Information on the product may change, please check the manufacturers website and page for the most up to date information, see the link at the top right of this page.