Features

- Eight 300 MSPS, 16-bit DAC channels

- 67 dB SFDR D/As

- 1Vpp output range

- Choice of DC coupled or AC coupled outputs

- DIO on P16 (19 differential pairs)

- Xilinx Artix-7 FPGA

- DDR3 Memory

- Programmable or external sample clock

- Synchronized system sampling using

- common reference clock and triggers

- Framed, software or external triggering

- Log acquisition timing and events

- Power management features

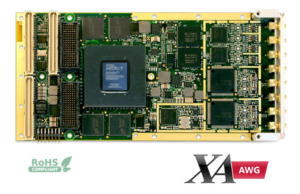

- PCI Express 2.0 XMC Module (75×150 mm)

- Use in any PCI Express desktop, compact PCI/PXI, PXIe, or cabled PCI Express application

- Drivers for Windows, Ubuntu (NVidia Xavier, TX2), Centos

Applications

- Wireless Transmitter

- RADAR

- Arbitary Waveform Generation

Useful resources on Youtube

These videos may be helpful in learning about using the FPGA on this board.

Overview

The XA-AWG is an XMC IO module featuring eight 16-bit, 300 MSPS DAC channels designed for high speed arbitrary waveform generation, wireless transmission, and RADAR pulse generation applications.

Flexible trigger methods include counted frames, software triggering and external triggering. The sample rate clock is either an external clock or on- board programmable PLL clock source.

Data acquisition control, signal processing, buffering, and system interface functions are implemented in a Xilinx Artix-7 FPGA device. Two 256Mx16 memories provide data buffering and FPGA computing memory.

The logic can be fully customized using VHDL and MATLAB using the FrameWork Logic toolset. The MATLAB BSP supports real-time hardware-in-the- loop development using the graphical, block diagram Simulink environment with Xilinx System Generator.

The PCI Express 2.0 interface supports continuous data rates up to 3200 MB/ s between the module and the host. A flexible data packet system implemented over the PCIe interface provides both high data rates to the host that is readily expandable for custom applications.

NVIDIA® Jetson GPU

The XA-AWG software support now includes drivers for development on the NVIDIA® Jetson TX2 GPU platform and the XVIDIA® Xavier that are aimed at Artificial Intelligence and is being increasing used in Photonics and Distributed Acoustic Sensing applications.

Dataflow

The board comes complete with working logic (Framework Logic) and software drivers (Malibu). Please see the data flow diagram.

The simplied data flow from Adc(s) to host application works as follows. Samples from the Adc(s) are clocked into the FPGA. The samples are packed where necessary for efficient use of the RAM chips. The RAM is used as a virtual FIFO to decouple the continuous stream of the Adc(s) from the block transfer nature of PCIe. The user application sets the packetsize. When a whole packet of data is available in the RAM, the PCIe DMA controller does a bus master transfer to the host memory. At configuration time the device drivers reserve physical memory for this purpose. When the transfer is complete, the DMA controller sends an interrupt to Malibu which then copies the packet from the busmaster area to virtual memory and then fires an event in the User application with a reference to the data.

The simplified data flow in the reverse direction for host to Dac(s) is similar. Onboard RAM is configured as a virtual FIFO between the PCIe and the Dac(s). When there is room in the RAM chips for a packet of samples, the PCIe DMA controller interrupts the host, which then signals the application to provide a packet of samples. The samples are copied from virtual memory to physical memory and then the PCIe DMA controller copies them into RAM. As data is flowed to the DAC(s) the RAM has more space for more packets and so the process is repeated.

On XA-TX the Dac memory is 1GB.

Support

The product comes with the following support items to help you with your project:

- Malibu Software, including

- Arb, Snap, Wave & Stream – example applications as sourcecode to setup the board for acquisition and waveform generation. Shows designer how to stream Adc samples to host file and stream from host to Dacs, written in C++.

- Drivers for Windows/Linux, 32 and 64 bit.

- Framework logic (source is extra cost)

- Makes the XMC board act as a data acquisition card, using onboard DDR as huge virtual FIFO’s.

- iiForum

- Knowledgebase of previous users of the XMC board.

- Access to the XMC engineers.

- Full hardware, software and firmware manuals as PDF.

- Telephone/email technical support from EnTegra Solutions and Innovative Integration.